- Conference proceedings

- © 2021

VLSI-SoC: Design Trends

28th IFIP WG 10.5/IEEE International Conference on Very Large Scale Integration, VLSI-SoC 2020, Salt Lake City, UT, USA, October 6–9, 2020, Revised and Extended Selected Papers

- Andrea Calimera ORCID: https://orcid.org/0000-0001-5881-3811 0 ,

- Pierre-Emmanuel Gaillardon ORCID: https://orcid.org/0000-0003-3634-3999 1 ,

- Kunal Korgaonkar ORCID: https://orcid.org/0000-0002-9078-2944 2 ,

- Shahar Kvatinsky ORCID: https://orcid.org/0000-0001-7277-7271 3 ,

- Ricardo Reis ORCID: https://orcid.org/0000-0001-5781-5858 4

Politecnico di Torino, Turin, Italy

You can also search for this editor in PubMed Google Scholar

University of Utah, Salt Lake City, USA

Technion – israel institute of technology, haifa, israel, universidade federal do rio grande do sul, porto alegre, brazil.

Part of the book series: IFIP Advances in Information and Communication Technology (IFIPAICT, volume 621)

Conference series link(s): VLSI-SoC: IFIP/IEEE International Conference on Very Large Scale Integration - System on a Chip

18k Accesses

11 Citations

6 Altmetric

Conference proceedings info: VLSI-SoC 2020.

- Table of contents

- Other volumes

About this book

Editors and affiliations, bibliographic information.

- Publish with us

Buying options

- Available as EPUB and PDF

- Read on any device

- Instant download

- Own it forever

- Compact, lightweight edition

- Dispatched in 3 to 5 business days

- Free shipping worldwide - see info

- Durable hardcover edition

Tax calculation will be finalised at checkout

Other ways to access

This is a preview of subscription content, log in via an institution to check for access.

Table of contents (16 papers)

Front matter, low-power high-speed adcs for adc-based wireline receivers in 22 nm fdsoi.

- David Cordova, Wim Cops, Yann Deval, François Rivet, Herve Lapuyade, Nicolas Nodenot et al.

Mixed-Mode Signal Processing for Implementing MCMC MIMO Detector

- Amin Aghighi, Behrouz Farhang-Boroujeny, Armin Tajalli

Low Power Current-Mode Relaxation Oscillators for Temperature and Supply Voltage Monitoring

- Shanshan Dai, Caleb R. Tulloss, Xiaoyu Lian, Kangping Hu, Sherief Reda, Jacob K. Rosenstein

Fully-Autonomous SoC Synthesis Using Customizable Cell-Based Analog and Mixed-Signal Circuits Generation

- Tutu Ajayi, Sumanth Kamineni, Morteza Fayazi, Yaswanth K. Cherivirala, Kyumin Kwon, Shourya Gupta et al.

Assessing the Configuration Space of the Open Source NVDLA Deep Learning Accelerator on a Mainstream MPSoC Platform

- Alessandro Veronesi, Davide Bertozzi, Milos Krstic

SAT-Based Mapping of Data-Flow Graphs onto Coarse-Grained Reconfigurable Arrays

- Yukio Miyasaka, Masahiro Fujita, Alan Mishchenko, John Wawrzynek

Learning Based Timing Closure on Relative Timed Design

- Tannu Sharma, Sumanth Kolluru, Kenneth S. Stevens

Multilevel Signaling for High-Speed Chiplet-to-Chiplet Communication

- Rakshith Saligram, Ankit Kaul, Muhannad S. Bakir, Arijit Raychowdhury

From Informal Specifications to an ABV Framework for Industrial Firmware Verification

- Samuele Germiniani, Moreno Bragaglio, Graziano Pravadelli

Modular Functional Testing: Targeting the Small Embedded Memories in GPUs

- Josie Esteban Rodriguez Condia, Matteo Sonza Reorda

RAT: A Lightweight Architecture Independent System-Level Soft Error Mitigation Technique

- Jonas Gava, Ricardo Reis, Luciano Ost

SANSCrypt: Sporadic-Authentication-Based Sequential Logic Encryption

- Yinghua Hu, Kaixin Yang, Shahin Nazarian, Pierluigi Nuzzo

3D Nanofabric: Layout Challenges and Solutions for Ultra-scaled Logic Designs

- Edouard Giacomin, Juergen Boemmels, Julien Ryckaert, Francky Catthoor, Pierre-Emmanuel Gaillardon

3D Logic Cells Design and Results Based on Vertical NWFET Technology Including Tied Compact Model

- Arnaud Poittevin, Chhandak Mukherjee, Ian O’Connor, Cristell Maneux, Guilhem Larrieu, Marina Deng et al.

Statistical Array Allocation and Partitioning for Compute In-Memory Fabrics

- Brian Crafton, Samuel Spetalnick, Gauthaman Murali, Tushar Krishna, Sung-Kyu Lim, Arijit Raychowdhury

abstractPIM: A Technology Backward-Compatible Compilation Flow for Processing-In-Memory

- Adi Eliahu, Rotem Ben-Hur, Ronny Ronen, Shahar Kvatinsky

Back Matter

Other volumes.

The 16 full papers included in this volume were carefully reviewed and selected from the 38 papers (out of 74 submissions) presented at the conference. The papers discuss the latest academic and industrial results and developments as well as future trends in the field of System-on-Chip (SoC) design, considering the challenges of nano-scale, state-of-the-art and emerging manufacturing technologies. In particular they address cutting-edge research fields like low-power design of RF, analog and mixed-signal circuits, EDA tools for the synthesis and verification of heterogenous SoCs, accelerators for cryptography and deep learning and on-chip Interconnection system, reliability and testing, and integration of 3D-ICs.

*The conference was held virtually.

- artificial intelligence

- communication systems

- computer hardware

- computer-aided design

- distributed computer systems

- distributed systems

- embedded systems

- field programmable gate array

- integrated circuits

- microprocessor chips

- network protocols

- parallel processing systems

- signal processing

- telecommunication systems

- vlsi circuits

Andrea Calimera

Pierre-Emmanuel Gaillardon

Kunal Korgaonkar, Shahar Kvatinsky

Ricardo Reis

Book Title : VLSI-SoC: Design Trends

Book Subtitle : 28th IFIP WG 10.5/IEEE International Conference on Very Large Scale Integration, VLSI-SoC 2020, Salt Lake City, UT, USA, October 6–9, 2020, Revised and Extended Selected Papers

Editors : Andrea Calimera, Pierre-Emmanuel Gaillardon, Kunal Korgaonkar, Shahar Kvatinsky, Ricardo Reis

Series Title : IFIP Advances in Information and Communication Technology

DOI : https://doi.org/10.1007/978-3-030-81641-4

Publisher : Springer Cham

eBook Packages : Computer Science , Computer Science (R0)

Copyright Information : IFIP International Federation for Information Processing 2021

Hardcover ISBN : 978-3-030-81640-7 Published: 15 July 2021

Softcover ISBN : 978-3-030-81643-8 Published: 15 July 2022

eBook ISBN : 978-3-030-81641-4 Published: 14 July 2021

Series ISSN : 1868-4238

Series E-ISSN : 1868-422X

Edition Number : 1

Number of Pages : XVIII, 364

Number of Illustrations : 70 b/w illustrations, 139 illustrations in colour

Topics : Computer Systems Organization and Communication Networks , Control Structures and Microprogramming , Input/Output and Data Communications , Information Systems Applications (incl. Internet)

Policies and ethics

Societies and partnerships

- Find a journal

- Track your research

- STM Journals

- Special Issues

- Conferences

- Editorial Board Members

- Reviewers Board Members

- Advisory Panel

- Indexing Bodies

- For Authors

- For Reviewers

- For Editors

- For Advisory Board

- Special Issue Guidelines

- Peer-Review Policy

- Publication Ethics and Virtue

- Manuscript Guidelines

- Article Processing Charge

- Editorial Policy

- Advertising Policy

- STM Website and Link Policy

- Distribution and dessemination of Research

- Informed consent Policy

"Connect with colleagues and showcase your academic achievements."

"Unleashing the potential of your words"

"Explore a vast collection of books and broaden your horizons."

"Empower yourself with the knowledge and skills needed to succeed."

"Collaborate with like-minded professionals and share your knowledge."

"Learn from experts and engage with a community of learners."

- ICDR Group of Companies

- Training Programs

Journal of VLSI Design Tools and Technology

Journal menu, editors overview.

Dr. Brajesh Kumar Kaushik

Professor Indian Institute of Technology, Roorkee Editor in Chief Journal of VLSI Design Tools and Technology

Institutional Profile Link : http://ece. . .

“Electrical Engineering”

Journal of VLSI Design Tools & Technology

Domino Logic Circuit

Fft processor, round robin arbiter, high-level synthesis for vlsi systems.

STM Journals, An imprint of Consortium e-Learning Network Pvt. Ltd. A-118, 1st Floor, Sector-63, Noida, U.P. India, Pin – 201301 E-mail: [email protected] (Tel) (+91) 0120- 4781 200 (Mob) (+91) 9810078958, +919667725932

Comparative Analysis of CMOS CNFET and Memristor Based Full Adder Circuits and CMOS Memristor Based Multiplexer Circuits

Design of Decoder Using Domino Logic Circuit for VLSI

Design and Simulation of Forging Die Towards Improving Life of Closed Die

About the Journal

Journal of VLSI Design Tools and Technology (jovdtt) : 2249-474X(e) is a peer-reviewed hybrid open-access journal launched in 2015 focused on the rapid publication of fundamental research papers on all areas of VLSI Design Tools & Technology. View Full Focus and Scope…

Journal Particulars

Special Issue

VLSI, Static CMOS, Dynamic CMOS, Domino logic, MOSFET, Simulation

Arithmetic Functions, Fast Fourier Transform, Round Robin Arbiter

Process stages, Lexical processing, Algorithm optimization, Control/Dataflow analysis, Library

To provide the best experiences, we and our partners use technologies like cookies to store and/or access device information. Consenting to these technologies will allow us and our partners to process personal data such as browsing behavior or unique IDs on this site and show (non-) personalized ads. Not consenting or withdrawing consent, may adversely affect certain features and functions.

Click below to consent to the above or make granular choices. Your choices will be applied to this site only. You can change your settings at any time, including withdrawing your consent, by using the toggles on the Cookie Policy, or by clicking on the manage consent button at the bottom of the screen.

WEBSITE DISCLAIMER

Last updated: 2022-06-15

The information provided by STM Journals (“Company”, “we”, “our”, “us”) on https://journals.stmjournals.com / (the “Site”) is for general informational purposes only. All information on the Site is provided in good faith, however, we make no representation or warranty of any kind, express or implied, regarding the accuracy, adequacy, validity, reliability, availability, or completeness of any information on the Site.

UNDER NO CIRCUMSTANCE SHALL WE HAVE ANY LIABILITY TO YOU FOR ANY LOSS OR DAMAGE OF ANY KIND INCURRED AS A RESULT OF THE USE OF THE SITE OR RELIANCE ON ANY INFORMATION PROVIDED ON THE SITE. YOUR USE OF THE SITE AND YOUR RELIANCE ON ANY INFORMATION ON THE SITE IS SOLELY AT YOUR OWN RISK.

EXTERNAL LINKS DISCLAIMER

The Site may contain (or you may be sent through the Site) links to other websites or content belonging to or originating from third parties or links to websites and features. Such external links are not investigated, monitored, or checked for accuracy, adequacy, validity, reliability, availability, or completeness by us.

WE DO NOT WARRANT, ENDORSE, GUARANTEE, OR ASSUME RESPONSIBILITY FOR THE ACCURACY OR RELIABILITY OF ANY INFORMATION OFFERED BY THIRD-PARTY WEBSITES LINKED THROUGH THE SITE OR ANY WEBSITE OR FEATURE LINKED IN ANY BANNER OR OTHER ADVERTISING. WE WILL NOT BE A PARTY TO OR IN ANY WAY BE RESPONSIBLE FOR MONITORING ANY TRANSACTION BETWEEN YOU AND THIRD-PARTY PROVIDERS OF PRODUCTS OR SERVICES.

PROFESSIONAL DISCLAIMER

The Site can not and does not contain medical advice. The information is provided for general informational and educational purposes only and is not a substitute for professional medical advice. Accordingly, before taking any actions based on such information, we encourage you to consult with the appropriate professionals. We do not provide any kind of medical advice.

Content published on https://journals.stmjournals.com / is intended to be used and must be used for informational purposes only. It is very important to do your analysis before making any decision based on your circumstances. You should take independent medical advice from a professional or independently research and verify any information that you find on our Website and wish to rely upon.

THE USE OR RELIANCE OF ANY INFORMATION CONTAINED ON THIS SITE IS SOLELY AT YOUR OWN RISK.

AFFILIATES DISCLAIMER

The Site may contain links to affiliate websites, and we may receive an affiliate commission for any purchases or actions made by you on the affiliate websites using such links.

TESTIMONIALS DISCLAIMER

The Site may contain testimonials by users of our products and/or services. These testimonials reflect the real-life experiences and opinions of such users. However, the experiences are personal to those particular users, and may not necessarily be representative of all users of our products and/or services. We do not claim, and you should not assume that all users will have the same experiences.

YOUR RESULTS MAY VARY.

The testimonials on the Site are submitted in various forms such as text, audio, and/or video, and are reviewed by us before being posted. They appear on the Site verbatim as given by the users, except for the correction of grammar or typing errors. Some testimonials may have been shortened for the sake of brevity, where the full testimonial contained extraneous information not relevant to the general public.

The views and opinions contained in the testimonials belong solely to the individual user and do not reflect our views and opinions.

ERRORS AND OMISSIONS DISCLAIMER

While we have made every attempt to ensure that the information contained in this site has been obtained from reliable sources, STM Journals is not responsible for any errors or omissions or the results obtained from the use of this information. All information on this site is provided “as is”, with no guarantee of completeness, accuracy, timeliness, or of the results obtained from the use of this information, and without warranty of any kind, express or implied, including, but not limited to warranties of performance, merchantability, and fitness for a particular purpose.

In no event will STM Journals, its related partnerships or corporations, or the partners, agents, or employees thereof be liable to you or anyone else for any decision made or action taken in reliance on the information in this Site or for any consequential, special or similar damages, even if advised of the possibility of such damages.

GUEST CONTRIBUTORS DISCLAIMER

This Site may include content from guest contributors and any views or opinions expressed in such posts are personal and do not represent those of STM Journals or any of its staff or affiliates unless explicitly stated.

LOGOS AND TRADEMARKS DISCLAIMER

All logos and trademarks of third parties referenced on https://journals.stmjournals.com / are the trademarks and logos of their respective owners. Any inclusion of such trademarks or logos does not imply or constitute any approval, endorsement, or sponsorship of STM Journals by such owners.

Should you have any feedback, comments, requests for technical support, or other inquiries, please contact us by email: [email protected] .

- Technologies

- Privacy Policy

Latest Research topics in vlsi design

Latest research topics in vlsi design.

If we narrow down our discussion to research in areas like electronics, electrical, computer science, artificial intelligence , wireless communication and related fields, which are the base of everything in this high-tech world. In these fields researchers have developed applications (aided with technology) for every field ranging from biomedical to aerospace and construction, which were nowhere related to electronics or even current.

As the research fields we are talking about are providing base to the developing world and providing it with reliable technologies which are being used in real time, the work of researcher becomes more wide starting with an idea to the realization of the idea in the real world in form of application or product.

To make a reliable and working model the idea of the VLSI design project ( i.e speech processing application, biomedical monitoring system etc) needs to be implemented and re-implemented, re-tested and improvised. The there are many development cycles and techniques available which eases up the implementation like:

- Behavioral simulation

- Software based model

- Hardware Implementation (ASIC)

- Programmable hardware (FPGA)

- Co-simulation

Behavioral simulation is used at initial phase and it is not appropriate for testing the real time behavior of the system in actual environment as it is more close to systems behavior in ideal environment.

We can simulate the actual environment by using different software models (more like software models of channels used to test communication systems) but its capabilities are also limited to human capability to model the environmental conditions in mathematical equations and models.

All of us are familiar with ASIC, their high performance and hardwired implementation. These are good for final implementation but not for intermediate stages of implementation and testing. Nothing is better than ASIC for real time testing of analog VLSI circuits. But for digital circuits and DSP applications we have a better option of FPGA (Field Programmable Gate Array).

The hardware co-simulation is a good idea to test and monitor systems in real time. To get more details about PhD thesis in VLSI you can do online research or contact us.

latest Low power research topics in vlsi design

The Research Support Centre provides expert advice and support across the whole Engineering and Technical research lifecycle, from discovery through exploitation of technical and translational research. The centre has two primary functions:

- i) to facilitate the delivery of the Engineering Sciences research strategy and to build partnerships andii) to bring together all the technical research management and support services for Students.

To achieve these goals the centre is made up of two inter-relating components. The Academic Research Support Centre consists of the Research Coordination Office, Platform Technologies team and a Translational Research Office. The Technical Research Support Centre is made up of the Joint Research Office.

The Research Support Centre encompasses a wide range of expertise and facilities. By coordinating these resources, we can provide researchers with a package of support that is integrated, high quality and streamlined – and clearly accountable.

Once a researcher has a proposal for high quality research that will benefit, they can access all the help and resources they need through one gateway. This includes support with the approval process and funding applications and help setting up technical trials.

VLSI PHD Projects

Our research interests cover low power processor architectures, low power circuit design techniques, analog and mixed signal circuit design, rapid prototyping of digital systems, reconfigurable processors, Digital arithmetic, advanced processor architectures, vlsi implementation of signal and image processing algorithms, testing verification, memory design, Embedded vlsi and asynchronous circuits.

Organization engaged with embedded commodity development and serving various business solutions such as

- Embedded System Product Development,

- Software services,

- Android development,

- Web development.

Description for “Ph.d guidance with project assitance” Ph.d/ M.Phil PROJECT ASSISTANCE We look forward to welcoming you to one of our “Research and Development Division” for all Ph.D., Research scholars. We will arrange you the following details for completing your Ph.d Degree

- Any University Admission- We provides a step-to-step guide to completing the application form, and will help make the process as straight forward as possible.

- Guide Arrangement

- Survey Paper Preparation

- Problem Identification –Problem Identification of Existing System.

- Implementation in all domains

- Mobile Ad hoc Networks

- Wireless Networks

- Image Processing

- Grid Computing

- Distributed Computing

- Natural Language Processing

- Cloud Computing

- Soft Computing

- Data Mining

- Wireless Senor Networks

Delivering effective support on your Ph. D work:

Companies represents a simple and practical advice on the problems of getting started, getting organized with the working on Ph.D projects.

We make you understand the practicalities of surviving the ordeal. We just make you divide the huge task into less challenging pieces. The training includes a suggested structure and a guide to what should go in each section.

We afford complete support with real-time exposure in your Ph.D works in the field of VLSI. Our Mission drives us in the way of delivering applications as well as products with complete integrity, innovative & interesting ideas with 100% accuracy.

- Assistance in ALL Stages of your PhD Research in VLSI from Topic Selection to Thesis Submission.

- Creating 100% confident in submitting your thesis work.

- Our experienced professionals support you in your research works.

- Providing complete solutions for the Research Scholars in many advanced domains.

Technologies used in VLSI:

- Modelsim 6.5b Simulator

- Xilinx ISE 10.1 System generator

III. Quartus 11.1

- Tanner v7 EDA tool

iii. W-Edit

- Microwind & DSCH v2

VII. P-spice

VIII. LT-spice

. Spartan IIIe

- Hardware Description Language

. Verilog HDL

CORE AREA OF GUIDANCE:

- Digital signal processing Vlsi

- Image processing Vlsi

III. Wireless Vlsi

- Communication Vlsi

- Testing Vlsi

- Digital cmos Vlsi

VII. low power Vlsi

VIII. Core Vlsi

- Memory Designs

PROJECT SUPPORT:

- Confirmation Letter

- Attendance Certificate

III. Completion Certificate

Preprocessing Work:

- Paper Selection

Identifying the problem:

- Screenshots

III. Simulation Report

- Synthesize Report

Report Materials:

- Block Diagrams

- Review Details

III. Relevant Materials

- Presentation

- Supporting Documents

- Software E-Books

VII. Software Development Standards & Procedure – E-Book

Learning Exposure:

VIII. Programming classes

- Practical training

- Project Design & Implementation

Publishing Support:

XII. Conference Support

XIII. Journal Support

XIV. Guide Arrangements

Vlsi based projects like image processing projects, low power projects, matlab with vlsi projects , cryptography projects, OFDM projects, SDR projects, communication projects, zigbee projects, digital signal processing projects, and also protocol interfacing projects like uart ,i2c,spi projects.

Signal and Image processing projects can be simulated by using Modelsim 6.5b and synthesized by Xilinx 10.1 using Spartan IIIe fpga and by Quartus 11.1using altera de2 fpga. In image processing projects, the input image or video can be converted to coefficients using Matlab. Low power projects can be designed using Tanner, Microwind and spice tools.

We spotlights on imparting an overall exposure to the concept and design methodologies of all major aspects of vlsi engineering relevant to industry needs and ground-breaking thoughts with 100% pure accuracy.

latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design low power testing bist latest research topics in vlsi design latest latest research topics in vlsi design area latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design latest research topics in vlsi design

cmos vlsi Recently Published Documents

Total documents.

- Latest Documents

- Most Cited Documents

- Contributed Authors

- Related Sources

- Related Keywords

Back propagation neural network based power estimation method for CMOS VLSI circuits

Low power vlsi design techniques: a review.

Since CMOS technology consumes less power it is a key technology for VLSI circuit design. With technologies reaching the scale of 10 nm, static and dynamic power dissipation in CMOS VLSI circuits are major issues. Dynamic power dissipation is increased due to requirement of high speed and static power dissipation is at much higher side now a days even compared to dynamic power dissipation due to very high gate leakage current and subthreshold leakage. Low power consumption is equally important as speed in many applications since it leads to a reduction in the package cost and extended battery life. This paper surveys contemporary optimization techniques that aims low power dissipation in VLSI circuits.

Design of low-power CMOS VLSI circuits using multi-objective optimization in genetic algorithms

This paper presents a design CAD tool for automated design of digital CMOS VLSI circuits. In order to fit the circuit performance into desired specifications, a multi-objective optimization approach based on genetic algorithms (GA) is proposed and the transistor sizes are calculated based on the analytical equations describing the behavior of the circuit. The optimization algorithm is developed in MATLAB and the performance of the designed circuit is verified using HSPICE simulations based on 0.18µm CMOS technology parameters. Different digital integrated circuits were successfully designed and verified using the proposed design tool. It is also shown in this paper that, the design results obtained from the proposed algorithm in MATLAB, have a very good agreement with the obtained circuit simulation results in HSPICE.

Technologies for creating radiation-resistant VLSI

The technology of radiation-resistant CMOS VLSI is based on industrial IC technology. The design uses feedback circuits and guard rings to compensate for single effects of cosmic particles (SEE). In most critical cases, these influences in digital circuits lead to single faults (SEU), which temporarily disrupt the state of memory cells, to latching (SEL), and in the long term to a catastrophic change of state. Various space programs confirm great prospects for their use in future space structures. The article discusses the effects of using radiation-resistant CMOS technology, technology based on a silicon-on-sapphire structure, CMOS technology on an insulating substrate taking into account typical characteristics, SIMOX-SOI technology, which consists in separation by implantation of oxygen ions. In new designs of circuits, more advanced algorithms should be implemented for the future.

Machine Learning Based Power Estimation for CMOS VLSI Circuits

Abstract The authors have requested that this preprint be withdrawn due to a need to make corrections.

Abstract Nowdays, machine learning (ML) algorithms are receiving massive attention in most of the engineering application since it has capability in complex systems modelling using historical data. Estimation of power for CMOS VLSI circuit using various circuit attributes is proposed using passive machine learning based technique. The proposed method uses supervised learning method which provides a fast and accurate estimation of power without affecting the accuracy of the system. Power estimation using random forest algorithm is relatively new. Accurate estimation of power of CMOS VLSI circuits is estimated by using random forest model which is optimized and tuned by using multi-objective NSGA-II algorithm. It is inferred from the experimental results testing error varies from 1.4 percent to 6.8 percent and in terms of and Mean Square Error is 1.46e-06 in random forest method when compared to BPNN. Statistical estimation like coefficient of determination (𝑅) and Root Mean Square Error (RMSE) are done and it is proven that random Forest is best choice for power estimation of CMOS VLSI circuits with high coefficient of determination of 0.99938. and low RMSE of 0.000116.

Leakage Power Reduction in CMOS VLSI Circuits using Advance Leakage Reduction Method

Recently, consumption of power is key problem of logic circuits based on Very Large Scale Integration. More potentiality consumption isn’t considered an appropriate for storage cell life for the use in cell operations and changes parameters such as optimality, efficiency etc, more consumption of power also provides for minimization of cell storage cycle. In present scenario static consumption of power is major troubles in logic circuits based on CMOS. Layout of drainage less circuit is typically complex. Several derived methods for minimization of consumption of potentiality for logic circuits based on CMOS. For this research paper, a technique called Advance Leakage reduction (AL reduction) is proposed to reduce the leakage power in CMOS logic circuits. To draw our structure circuit related to CMOS like Inverter, inverted AND, and NOR etc. we have seen the power and delay for circuits. This paper incorporates, analyzing of several minimization techniques as compared with proposed work to illustrate minimization in ratio of energy and time usage and time duration for propagation. LECTOR, Source biasing, Stack ONOFIC method is observed and analyzed with the proposed method to evaluate the leakage power consumption and propagation delay for logic circuits based on CMOS. Entire work has done in LT Spice Software with 180nm library of CMOS.

Revisiting the Utility of Transmission Gate and Passtransistor Logic Styles in CMOS VLSI Design

Peculiarities of appearance and registration of the latchup in cmos vlsi under uniform pulsed laser irradiation, export citation format, share document.

Georgia Tech Faculty to Present Timely Topics at VLSI Symposium on Technology and Circuits

May 19, 2022 — atlanta, ga.

In June, some of the world’s top technologists in the VLSI (Very Large-Scale Integration) industry will convene in Honolulu for the 2022 IEEE Symposium on VLSI Technology and Circuits , one of the premier symposiums for microelectronics and semiconductor research. Now in its 42 nd year, the VLSI Symposium offers attendees the opportunity to share and exchange ideas on the most relevant subjects in their fields and address current and future directions in the development of VLSI technology.

Given the continuing global semiconductor shortage, the theme of this year’s conference is “Technology and Circuits for the Critical Infrastructure of the Future.” Seven papers submitted by Georgia Tech faculty have been accepted and will be presented during the conference. Paper topics include Ferroelectric Memories, Resistive Memories, Embedded DRAM, and Power Converter based on GaN/Si. The contributing professors include Asif Khan, Arijit Raychowdhury, Shimeng Yu, and Suman Datta from Georgia Tech’s Institute of Electronics and Nanotechnology (IEN) and the School of Electrical and Computer Engineering (ECE).

In addition to presenting their papers, Datta and Yu are also organizing short courses on Monolithic and Heterogenous Integration and Advances in Application-Specific Computing Systems and Technologies. Muhannad Bakir will present on “2.5D and 3D Polylithic Integration Technologies” as part of the course on Monolithic and Heterogenous Integration.

“The VLSI Symposium is one of the most selective and prestigious venues to publish the latest advances in semiconductor technologies and circuits, and it has always had a strong industry presence,” said Raychowdhury, who also serves as the Steve W. Chaddick School Chair in ECE. “Our participation through multiple papers and invited talks is a clear testament of the depth and breadth of our research program. Congratulations to all of the students and faculty members who are making us proud through their impactful research.”

About the contributors:

Arijit Raychowdhury is the Steve W. Chaddick School Chair and Professor at ECE. His research interests include low power digital and mixed-signal circuit design, design of power converters, sensors and exploring interactions of circuits with device technologies. He holds more than 25 U.S. and international patents and has published over 80 articles in journals and refereed conferences. He holds a Ph.D. in electrical and computer engineering from Purdue University and a B.E. in electrical and telecommunication engineering from Jadavpur University in India.

Muhannad Bakir is the Dan Fielder Professor in ECE. His research interests include heterogeneous microsystem design and integration, including 2.5D and 3D ICs and packaging, advanced cooling and power delivery for emerging system architectures; electrical and photonic interconnect technologies; biosensor technologies and their integration with CMOS; and nanofabrication technologies. Bakir is an editor of IEEE Transactions on Electron Devices and an associate editor of IEEE Transactions on Components , Packaging and Manufacturing Technology.

Suman Datta will join the Georgia Tech faculty this fall as Joseph M. Pettit Chair in ECE and a Georgia Research Alliance (GRA) Eminent Scholar. He will also have a joint appointment with the School of Materials Science and Engineering (MSE). His research involves high-performance, heterogenous computing, brain-inspired computing, and collective state computing using advanced CMOS (complementary metal–oxide–semiconductor) and beyond-CMOS devices. He also focuses on the development of semiconductor technologies for other types of computing, including intermittent computing, cryogenic computing, and harsh environment computing.

Asif Khan is an assistant professor in ECE with a courtesy appointment in MSE. His research focuses on microelectronic devices, specifically on ferroelectric devices that address the challenges faced by the semiconductor industry due to the end of transistor miniaturization. His research group at Georgia Tech focuses on all aspects of ferroelectricity ranging from materials physics, growth, and electron microscopy to micro- and nano-fabrication of electronic devices, all the way to ferroelectric circuits and systems for artificial intelligence, machine learning, and data-centric applications.

Shimeng Yu is an associate professor in ECE. He has both a master’s and Ph.D. in electrical engineering from Stanford University and a B.S. in microelectronics from Peking University. His research interests lie in nanoelectronic devices and circuits for energy-efficient computing systems. His expertise is on the emerging non-volatile memories (e.g., RRAM, ferroelectrics) for different applications such as deep learning accelerator, neuromorphic computing, monolithic 3D integration, and hardware security.

The IEEE Symposium on VLSI Technology and Circuits is a five-day hybrid event known as the microelectronics industry’s premiere international conference integrating technology, circuits, and systems with a range and scope unlike any other conference. In addition to the technical presentations, the Symposium program will feature a demonstration session, evening panel discussions, joint focus sessions, short courses, workshops, and a special forum session that provides a focused discussion on a specific topic relevant to the Symposia theme. To learn more visit http://www.vlsisymposium.org .

Laurie Haigh

IEEE Account

- Change Username/Password

- Update Address

Purchase Details

- Payment Options

- Order History

- View Purchased Documents

Profile Information

- Communications Preferences

- Profession and Education

- Technical Interests

- US & Canada: +1 800 678 4333

- Worldwide: +1 732 981 0060

- Contact & Support

- About IEEE Xplore

- Accessibility

- Terms of Use

- Nondiscrimination Policy

- Privacy & Opting Out of Cookies

A not-for-profit organization, IEEE is the world's largest technical professional organization dedicated to advancing technology for the benefit of humanity. © Copyright 2024 IEEE - All rights reserved. Use of this web site signifies your agreement to the terms and conditions.

Suggestions or feedback?

MIT News | Massachusetts Institute of Technology

- Machine learning

- Social justice

- Black holes

- Classes and programs

Departments

- Aeronautics and Astronautics

- Brain and Cognitive Sciences

- Architecture

- Political Science

- Mechanical Engineering

Centers, Labs, & Programs

- Abdul Latif Jameel Poverty Action Lab (J-PAL)

- Picower Institute for Learning and Memory

- Lincoln Laboratory

- School of Architecture + Planning

- School of Engineering

- School of Humanities, Arts, and Social Sciences

- Sloan School of Management

- School of Science

- MIT Schwarzman College of Computing

Second round of seed grants awarded to MIT scholars studying the impact and applications of generative AI

Press contact :.

Previous image Next image

Last summer, MIT President Sally Kornbluth and Provost Cynthia Barnhart issued a call for papers to “articulate effective roadmaps, policy recommendations, and calls for action across the broad domain of generative AI.” The response to the call far exceeded expectations with 75 proposals submitted. Of those, 27 proposals were selected for seed funding .

In light of this enthusiastic response, Kornbluth and Barnhart announced a second call for proposals this fall.

“The groundswell of interest and the caliber of the ideas overall made clear that a second round was in order,” they said in their email to MIT’s research community this fall. This second call for proposals resulted in 53 submissions.

Following the second call, the faculty committee from the first round considered the proposals and selected 16 proposals to receive exploratory funding. Co-authored by interdisciplinary teams of faculty and researchers affiliated with all five of the Institute’s schools and the MIT Schwarzman College of Computing, the proposals offer insights and perspectives on the potential impact and applications of generative AI across a broad range of topics and disciplines.

Each selected research group will receive between $50,000 and $70,000 to create 10-page impact papers. Those papers will be shared widely via a publication venue managed and hosted by the MIT Press under the auspices of the MIT Open Publishing Services program.

As with the first round of papers, Thomas Tull, a member of the MIT School of Engineering Dean’s Advisory Council and a former innovation scholar at the School of Engineering, contributed funding to support the effort.

The selected papers are:

- “A Road-map for End-to-end Privacy and Verifiability in Generative AI,” led by Alex Pentland, Srini Devadas, Lalana Kagal, and Vinod Vaikuntanathan;

- “A Virtuous Cycle: Generative AI and Discovery in the Physical Sciences,” led by Philip Harris and Phiala Shanahan;

- “Artificial Cambrian Intelligence: Generating New Forms of Visual Intelligence,” led by Ramesh Raskar and Tomaso A. Poggio;

- “Artificial Fictions and the Value of AI-Generated Art,” led by Justin Khoo;

- “GenAI for Improving Human-to-human Interactions with a Focus on Negotiations,” led by Lawrence Susskind and Samuel Dinnar;

- “Generative AI as a New Applications Platform and Ecosystem,” led by Michael Cusumano;

- “Generative AI for Cities: A Civic Engagement Playbook,” led by Sarah Williams, Sara Beery, and Eden Medina;

- “Generative AI for Textile Engineering: Advanced Materials from Heritage Lace Craft,” led by Svetlana V. Boriskina;

- “Generative AI Impact for Biomedical Innovation and Drug Discovery,” led by Manolis Kellis, Brad Pentelute, and Marinka Zitnik;

- “Impact of Generative AI on the Creative Economy,” led by Ashia Wilson and Dylan Hadfield-Menell;

- “Redefining Virtuosity: The Role of Generative AI in Live Music Performances,” led by Joseph A. Paradiso and Eran Egozy;

- “Reflection-based Learning with Generative AI,” led by Stefanie Mueller;

- “Robust and Reliable Systems for Generative AI,” led by Shafi Goldwasser, Yael Kalai, and Vinod Vaikuntanathan;

- “Supporting the Aging Population with Generative AI,” led by Pattie Maes;

- “The Science of Language in the Era of Generative AI,” led by Danny Fox, Yoon Kim, and Roger Levy; and

- “Visual Artists, Technological Shock, and Generative AI,” led by Caroline Jones and Huma Gupta.

Share this news article on:

Related links.

- President Sally Kornbluth

- Office of the Provost

Related Topics

- Artificial intelligence

- Technology and society

- Technology and policy

- Computer science and technology

- Administration

- School of Architecture and Planning

- Electrical Engineering & Computer Science (eecs)

- School of Humanities Arts and Social Sciences

Related Articles

MIT scholars awarded seed grants to probe the social implications of generative AI

Previous item Next item

More MIT News

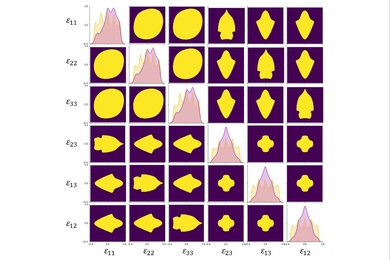

A first-ever complete map for elastic strain engineering

Read full story →

“Life is short, so aim high”

Shining a light on oil fields to make them more sustainable

MIT launches Working Group on Generative AI and the Work of the Future

Atmospheric observations in China show rise in emissions of a potent greenhouse gas

VIAVI Solutions joins MIT.nano Consortium

- More news on MIT News homepage →

Massachusetts Institute of Technology 77 Massachusetts Avenue, Cambridge, MA, USA

- Map (opens in new window)

- Events (opens in new window)

- People (opens in new window)

- Careers (opens in new window)

- Accessibility

- Social Media Hub

- MIT on Facebook

- MIT on YouTube

- MIT on Instagram

School of Electrical and Computer Engineering

College of engineering, georgia tech faculty to present timely topics at vlsi symposium on technology and circuits.

In June, some of the world’s top technologists in the VLSI industry will convene in Honolulu for one of the premier symposiums for microelectronics and semiconductor research.

In June, some of the world’s top technologists in the VLSI (Very Large-Scale Integration) industry will convene in Honolulu for the 2022 IEEE Symposium on VLSI Technology and Circuits , one of the premier symposiums for microelectronics and semiconductor research. Now in its 42 nd year, the VLSI Symposium offers attendees the opportunity to share and exchange ideas on the most relevant subjects in their fields and address current and future directions in the development of VLSI technology.

Given the continuing global semiconductor shortage, the theme of this year’s conference is “Technology and Circuits for the Critical Infrastructure of the Future.” Seven papers submitted by Georgia Tech faculty have been accepted and will be presented during the conference. Paper topics include Ferroelectric Memories, Resistive Memories, Embedded DRAM, and Power Converter based on GaN/Si. The contributing professors include Asif Khan, Arijit Raychowdhury, Shimeng Yu, and Suman Datta from Georgia Tech’s Institute of Electronics and Nanotechnology (IEN) and the School of Electrical and Computer Engineering (ECE).

In addition to presenting their papers, Datta and Yu are also organizing short courses on Monolithic and Heterogenous Integration and Advances in Application-Specific Computing Systems and Technologies. Muhannad Bakir will present on “2.5D and 3D Polylithic Integration Technologies” as part of the course on Monolithic and Heterogenous Integration.

“The VLSI Symposium is one of the most selective and prestigious venues to publish the latest advances in semiconductor technologies and circuits, and it has always had a strong industry presence,” said Raychowdhury, who also serves as the Steve W. Chaddick School Chair in ECE. “Our participation through multiple papers and invited talks is a clear testament of the depth and breadth of our research program. Congratulations to all of the students and faculty members who are making us proud through their impactful research.”

About the contributors:

Arijit Raychowdhury is the Steve W. Chaddick School Chair and Professor at ECE. His research interests include low power digital and mixed-signal circuit design, design of power converters, sensors and exploring interactions of circuits with device technologies. He holds more than 25 U.S. and international patents and has published over 80 articles in journals and refereed conferences. He holds a Ph.D. in electrical and computer engineering from Purdue University and a B.E. in electrical and telecommunication engineering from Jadavpur University in India.

Muhannad Bakir is the Dan Fielder Professor in ECE. His research interests include heterogeneous microsystem design and integration, including 2.5D and 3D ICs and packaging, advanced cooling and power delivery for emerging system architectures; electrical and photonic interconnect technologies; biosensor technologies and their integration with CMOS; and nanofabrication technologies. Bakir is an editor of IEEE Transactions on Electron Devices and an associate editor of IEEE Transactions on Components , Packaging and Manufacturing Technology.

Suman Datta will join the Georgia Tech faculty this fall as Joseph M. Pettit Chair in ECE and a Georgia Research Alliance (GRA) Eminent Scholar. He will also have a joint appointment with the School of Materials Science and Engineering (MSE). His research involves high-performance, heterogenous computing, brain-inspired computing, and collective state computing using advanced CMOS (complementary metal–oxide–semiconductor) and beyond-CMOS devices. He also focuses on the development of semiconductor technologies for other types of computing, including intermittent computing, cryogenic computing, and harsh environment computing.

Asif Khan is an assistant professor in ECE with a courtesy appointment in MSE. His research focuses on microelectronic devices, specifically on ferroelectric devices that address the challenges faced by the semiconductor industry due to the end of transistor miniaturization. His research group at Georgia Tech focuses on all aspects of ferroelectricity ranging from materials physics, growth, and electron microscopy to micro- and nano-fabrication of electronic devices, all the way to ferroelectric circuits and systems for artificial intelligence, machine learning, and data-centric applications.

Shimeng Yu is an associate professor in ECE. He has both a master’s and Ph.D. in electrical engineering from Stanford University and a B.S. in microelectronics from Peking University. His research interests lie in nanoelectronic devices and circuits for energy-efficient computing systems. His expertise is on the emerging non-volatile memories (e.g., RRAM, ferroelectrics) for different applications such as deep learning accelerator, neuromorphic computing, monolithic 3D integration, and hardware security.

The IEEE Symposium on VLSI Technology and Circuits is a five-day hybrid event known as the microelectronics industry’s premiere international conference integrating technology, circuits, and systems with a range and scope unlike any other conference. In addition to the technical presentations, the Symposium program will feature a demonstration session, evening panel discussions, joint focus sessions, short courses, workshops, and a special forum session that provides a focused discussion on a specific topic relevant to the Symposia theme. To learn more visit http://www.vlsisymposium.org .

IMAGES

VIDEO

COMMENTS

Explore the latest full-text research PDFs, articles, conference papers, preprints and more on VLSI TECHNOLOGY. Find methods information, sources, references or conduct a literature review on VLSI ...

The current research in VLSI explores emerging trends and novel ideas and concepts covering a broad range of topics in the area of VLSI: from VLSI circuits, systems, and design methods, to system-level design and systemon- chip issues, to bringing VLSI methods to new areas and technologies such as nano and molecular devices, MEMS, and quantum computing. Future design methodologies are also key ...

The development of complementary metal-oxide-semiconductor (CMOS) technology brought about a new paradigm for low-power circuit design. For the implementation of digital circuits with very large-scale integration, CMOS design styles are frequently employed in VLSI. There are billions of transistors on a single die in today's IC devices.

Different areas of VLSI Technology reviewed in the paper. This work thoroughly attempts to summarize the literature on AI/ML algorithms for VLSI design and modeling at different abstraction levels. It is the first paper that provides a detailed review encompassing circuit modeling to system-on-chip (SoC) design, along with physical design ...

The impact of AI on VLSI design was first demonstrated in 1985 by Robert. S. Kirk [15]. He briefly explained the scope and necessity for AI techniques in CAD tools at different levels of VLSI design. His paper included a brief on the existing VLSI-AI tools and stressed the importance of

The VLSI-SoC 2020 proceedings present cutting-edge research on very large scale integration, low-power design of RF, and more. VLSI-SoC: Design Trends: 28th IFIP WG 10.5/IEEE International Conference on Very Large Scale Integration, VLSI-SoC 2020, Salt Lake City, UT, USA, October 6-9, 2020, Revised and Extended Selected Papers | SpringerLink

This paper examines the impact of VLSI technology on the evolution of computer architecture and projects the future of this evolution. We see that over the past 20 years, the increased density of VLSI chips was applied to close the gap between microprocessors and high-end CPUs. Today this gap is fully closed and adding devices to uniprocessors is well beyond the point of diminishing returns ...

This Special Issue solicits original and unpublished papers on high-performance and low-power VLSI architectures and the relevant algorithmic optimizations in the field of wireless communications and digital signal processing. The topics of interest include but are not limited to: VLSI architectures for 5G and 6G telecommunications;

This research article provides an insight about the important challenges involved in the low power analog system design using advanced CMOS VLSI approach. Reduction in the dimension of MOS base channel and reduction in gate oxide results in greater advancement in terms of area of the chip, operating speed, and reduction of power consumption (mainly in digital components). In other words, few ...

The focus of this Special Issue is on the research challenges related to the design of emerging microelectronics and VLSI circuits and systems that meet the demanding specifications of innovative applications. This Special Issue considers challenges in the fields of low power consumption, small integration area, testing and security, without ...

Journal of VLSI Design Tools and Technology. ISSN: 2249-474X. Join As Reviewer. Submit a Topic. Subscribe Journal. E-mail: VLSI Design Tools & Technology. Comparative Analysis of CMOS CNFET and Memristor Based Full Adder Circuits and CMOS Memristor Based Multiplexer Circuits. VLSI Design Tools & Technology.

We invite researchers from various fields to present their research papers, reviews, and perspectives regarding VLSI and microelectronic-embedded circuits for IoT-assisted business accounts. The list of potential topics for this Special Issue includes, but is not limited to, the following:

Read all the papers in 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) | IEEE Conference | IEEE Xplore

Therefore, a new mindset is required for VLSI design to implement the IoT application. This chapter describes the first conventional technology used in VLSI design. Afterward, the characteristics ...

latest research topics in vlsi design. latest research topics in vlsi design - Doctor of philosophy is the final degree in any area. It requires a lot of efforts and hard work to achieve this.It starts with selection of a topic which should be recent and lies in your area of interest. If we talk specifically about research in technology then ...

Cmos Vlsi. Since CMOS technology consumes less power it is a key technology for VLSI circuit design. With technologies reaching the scale of 10 nm, static and dynamic power dissipation in CMOS VLSI circuits are major issues. Dynamic power dissipation is increased due to requirement of high speed and static power dissipation is at much higher ...

In June, some of the world's top technologists in the VLSI (Very Large-Scale Integration) industry will convene in Honolulu for the 2022 IEEE Symposium on VLSI Technology and Circuits, one of the premier symposiums for microelectronics and semiconductor research. Now in its 42nd year, the VLSI Symposium offers attendees the opportunity to share and exchange ideas on the most relevant ...

The focus of this Special Issue is on the research challenges related to the design of emerging microelectronics and VLSI circuits and related systems that meet the demanding specifications of innovative applications. This Special Issue considers challenges in the fields of low power consumption, small integration areas, testing and security ...

Read all the papers in 2023 International VLSI Symposium on Technology, Systems and Applications (VLSI-TSA/VLSI-DAT) | IEEE Conference | IEEE Xplore

VLSI design in biomedicine produces reduction in size of the chips, range, and speed enhancement. In this analysis, various proposals are scrutinized for VLSI employment of neural networks which ...

Those papers will be shared widely via a publication venue managed and hosted by the MIT Press under the auspices of the MIT Open Publishing Services program. As with the first round of papers, Thomas Tull, a member of the MIT School of Engineering Dean's Advisory Council and a former innovation scholar at the School of Engineering ...

In June, some of the world's top technologists in the VLSI (Very Large-Scale Integration) industry will convene in Honolulu for the 2022 IEEE Symposium on VLSI Technology and Circuits, one of the premier symposiums for microelectronics and semiconductor research.Now in its 42 nd year, the VLSI Symposium offers attendees the opportunity to share and exchange ideas on the most relevant ...